# **FPGA IP Core**

### 3D LUT Colour Correction & Processing

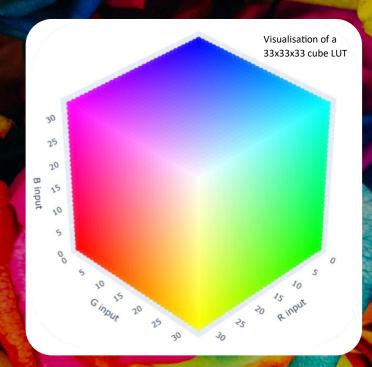

This IP core uses a three-dimensional look-up-table (3D LUT) for use in a video pipeline to manipulate colours in real time. Use cases include colour grading, colour correction, chroma keying, camera and screen calibration, and optional colour space conversion. The LUT can be loaded with values from standard tools or updated from your own software via an AMBA® 4 AXI-Lite interface.

#### **Features**

- Supports all common formats including 4Kp60

- Less than one line of latency

- LUT reprogramming on the fly

- Tetrahedral interpolation

- Configurable LUT size

- Works in AMD Vivado™ IP Integrator

- Uses AMBA 4 AXI-Stream Video

- Uses standardised '. cube' file formats

Optional extensions include:

Pre/post RGB ⇔ YCbCr conversion

### **Benefits**

Easy to integrate using either RTL or AMD's block design flow, this highly configurable core delivers maximum functionality for minimum integration effort. Its tetrahedral interpolation provides faithful conversion resulting in high image quality. The core has been optimised for resource utilisation and timing closure, not only through efficient implementation but also through a carefully considered pipeline architecture.

### **Demonstration**

A demonstration is available to show the effect of introducing a LUT to your workflow in an HDMI pipeline. This runs on a ZCU104 Zynq™ development board and uses AMD's HDMI 2.0 core to process RGB video up to 4K60.

### **Deliverables**

The delivery package consists of:

- Encrypted Netlist or Encrypted RTL

- AMD IP Integration package

- Includes '. cube' file conversion utility

- Product guide

## **FPGA IP Core**

### Resource Utilisation Guide

| Pixels In<br>Parallel | Input Bit<br>Depth | Output Bit<br>Depth | 3D LUT<br>Size  | LUT<br>Width | RAMB36E | CLB LUTs | CLB<br>Register |

|-----------------------|--------------------|---------------------|-----------------|--------------|---------|----------|-----------------|

| Single Buffer         |                    |                     |                 |              |         |          |                 |

| 2                     | 8                  | 10                  | 17 <sup>3</sup> | 10           | 15      | 5889     | 7263            |

| 2                     | 8                  | 10                  | 33 <sup>3</sup> | 10           | 35      | 5015     | 6143            |

| 2                     | 8                  | 10                  | 65 <sup>3</sup> | 10           | 265     | 4241     | 5129            |

| 4                     | 8                  | 10                  | 17 <sup>3</sup> | 10           | 30      | 11591    | 13515           |

| 4                     | 8                  | 10                  | 33 <sup>3</sup> | 10           | 70      | 9871     | 11265           |

| 2                     | 10                 | 10                  | 33 <sup>3</sup> | 10           | 35      | 7213     | 8835            |

| Double Buffer         |                    |                     |                 |              |         |          |                 |

| 2                     | 10                 | 10                  | 33 <sup>3</sup> | 10           | 70      | 9239     | 10611           |

Spartan™ 7 FPGAs, Artix™ 7 FPGAs

100MHz target clock (74.25MHz required for 1080p60 @ 2PPC over SDI)

Kintex™ 7/Ultrascale™/Ultrascale+™ FPGAs, Zynq™ Ultrascale+ MPSoC, and Artix Ultrascale+ FPGAs

300MHz target clock (297MHz required for 2160p60 @ 2PPC over SDI)

Performance subject to individual use-case and FPGA utilisation, congestion, and speed grade.

The symbol "3" refers to the LUT being a cube. For example, a 173 LUT consists of 17x17x17 values.

### **Video Formats**

Operations are performed at a pixel level, so image size and frame rate determine the necessary clock speed of the IP. The utilisation figures above are based on a clock speed of 300MHz, which is sufficient to handle 4K at 60 fps with a single instance. If a clock rate sufficient for a larger size or higher frame rate cannot be achieved, multiple instances of this block may be used in parallel.

### **About ITDev**

Formed in 2000, ITDev have been developing FPGA video solutions for more than 15 years. Having operated in a range of markets including pro AV, broadcast, aerospace, security and healthcare, we're well placed to provide integration support, or even full product development.

You can find more information, including testimonials on our website at www.itdev.co.uk.

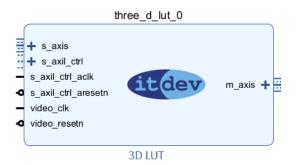

### **Example Block Diagram Interfaces**

Disclaimer This product brief is for informational purposes only. The information in this product brief is provided "as is" without warranty of any kind, either express or implied, including but not limited to the implied warranties of merchantability, fitness for aparticular purpose, or noninfringement. This product brief may contain technical inaccuracies or typographical errors. The information contained in this product brief may be changed at any time without prior notice. In no event shall I.T. Dev Ltd. be liable for any damages whatsoever, including but not limited to direct, indirect, special, incidental, or consequential damages, arising out of or in connection with the use or inability to use the information contained in this product brief. This product brief may contain information related to intellectual property rights, including patents trademarks, and copyrights. No license, express or implied, is granted by this product brief or by any information contained herein with respect to any intellectual property rights. All product names, logos, and brands are property of their respective owners. Use of these names, logos, and brands does not imply endorsement or affiliation. This product brief is governed by the laws of England and Wales, and any disputes arising out of or in connection with this product brief shall be subject to the exclusive jurisdiction of the courts of England and Wales. By using the information contained in this product brief, you agree to indemnify, defend, and hold harmless the author and the publisher from and against any and all claims, damages, liabilities, costs, and expenses, including reasonable attorneys' fees, arising out of or in connection with your use of the information contained in this product brief.