Aerospace compliant FPGA design

Client: Avionics equipment supplier

Client outcome: New proven trusted supplier

Summary

Our client had seen an opportunity to address a market opening through global expansion. They needed to build a new design team to develop the next product in their avionics product range. Typical of many companies in the UK, they were struggling to recruit high calibre engineers.

The client wanted to outsource some of their FPGA design work for the next product while they continued their recruitment drive. The identified IP block to outsource was on the critical path and they needed to have a design which could meet aerospace certification.

The client received the critical IP block on time and was able to handover further parts of the design. Their requirements had been refined in line with their expectations. The final delivery met the client’s aim of aerospace compliance.

In final project feedback the client was pleased to note they now had a new 'proven capable supplier'.

Situation

The client was building a new design team in the UK, to address a market opportunity. Whilst engaging in a recruitment programme they needed to outsource some critical FPGA IP development. The IP was to be integrated into a new product as part of their avionics product range.

The client did not have enough engineering resources to begin development and were concerned further delay would impact their ability to meet timescales.

Requirements were at an early stage and needed further refining. The main hardware platform was still in development, although early prototype boards were available for testing. The client’s main contact point had limited availability due to heavy travel plans.

-

Engineering resource restrictions

-

High level requirements needed refining

-

On target testing and verification

Key Issues

The requirements were only partially formed at the beginning of the project, and the hardware platform, to be used for testing and validation, was still in development when the project began. The system required ED-112 certification, which meant that many of the design elements were safety sensitive and had tight requirements.

The client would frequently be travelling between their international office locations and was likely to be out of contact for periods of time. This meant as a supplier we would need to operate with a reasonable degree of independence and would be counted upon to make good design decisions in the absence of direct instructions. Due to limited time availability of the client it would be essential to keep up fast, clear and concise communications.

-

ED-112 certification

-

Hardware platform still in development

-

Communication challenges

ITDev Contributions

Our FPGA engineers had existing experience interfacing FPGAs with asynchronous chips and were confident with how to proceed. Design and development of the functionality to store data on the Micron NAND flash memory was delivered to the customer well within the predicted time frame, exceeding the target write speeds and was verified thoroughly before delivery. As the relationship developed, the scope of our involvement increased, and we assigned more engineers to the project.

Visibility and traceability were key requirements for the certification. Communications were formally recorded in newly created tickets or updates to existing ones.

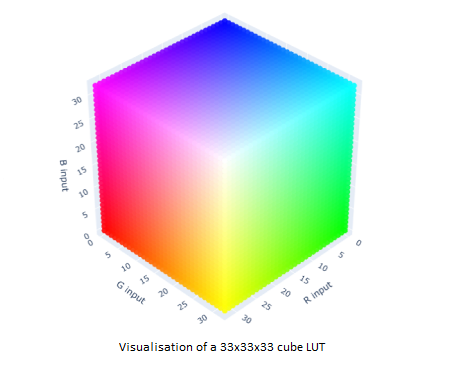

When developing IP, our preference is to utilise Continuous Integration and, to speed the deployment of this, we used our ACI (Accelerated CI) service. The resultant platform included an automated build and test procedure, which activated whenever a change was made to the repository.

Over 250 individual system and unit tests were implemented as part of the verification activity in the CI environment. With our commitment to openness, the client benefited from shared access to this environment. This included access to all current and historical test results.

During the verification stage, support was provided to the client on debugging using screen sharing. Additional debug support was provided via remote access to tools like SignalTap. Site visits were reserved for solving key issues working directly with the client.

Despite only having high level requirements, the client received a solution in line with their expectations.

-

VHDL implementation, mixed language (Verilog and VHDL) simulation

-

Exceeded target write speeds for the NAND flash interface

-

Openness and visibility at all stages of design

-

Agile Kanban approach to managing tasks

-

Assistance via remote access and client site visits

Client Benefits

The critical IP block was received on time. Requirements had been refined in line with expectations.

The client was able to focus on final product verification, as we went on to deliver the complete FPGA implementation.

The final delivery met aerospace compliance.

The client was able to progress internal recruitment and still deliver the next product on time.

In final project feedback the client was pleased to note they now had a new 'proven capable supplier'.

-

On time delivery

-

Aerospace compliance

-

Trusted 'proven capable supplier'

ITDev was pleased to support aerospace certification of this product and continues to provide our client with technical help.

If you have a project you would like to discuss with us, please get in contact. We will assess if there is a conflict of interest before continuing any discussion.