As discussed in my previous blog the VPK120 development board is loud if the fan is constantly running at top speed.

We have already discussed how to check if the board has the latest Linux code supporting the speed controller, I will now document how to add the minimal IP to send the necessary SYSMON data.

Step 3 – Configure the Versal to send the SYSMON data to the System Controller

The steps below are for a basic design that will add the minimal amount of IP required for the SYSMON data to be sent. if larger projects are required this can be used as a base and the CIPs IP can be customised as required as long as the settings shown in the sections below are unchanged.

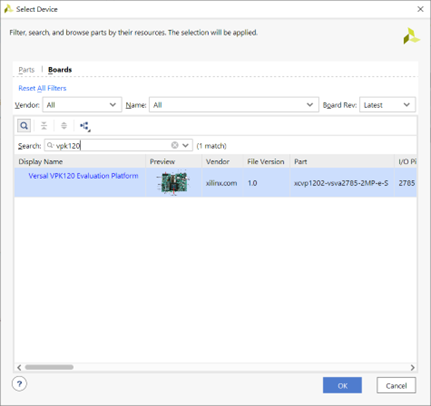

Create a new Vivado project setting the board part:

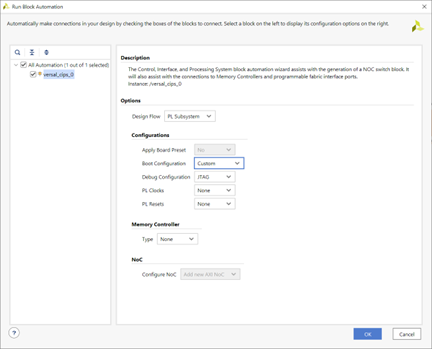

Create a new block design and add a CIPs IP and then “Run Block Automation”.

Select the Design Flow as PL Subsystem and add PL Clocks and PL Resets as required.

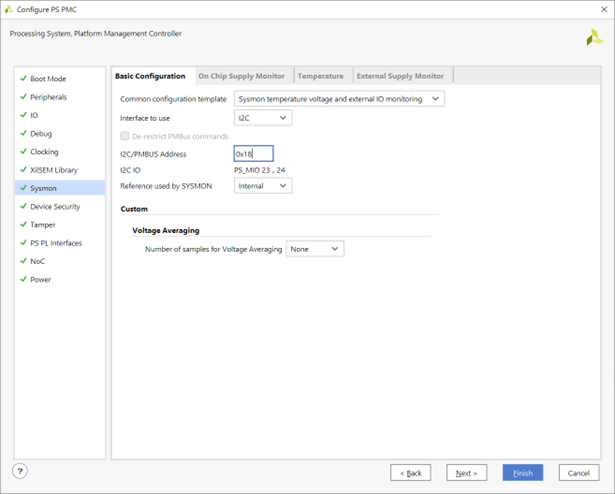

Open the IP block, click next and go into the PS PMC block.

Go to the Sysmon tab and set the Common configuration template to Sysmon temperature voltage and external IO monitoring, set the interface to use to I2C and the I2C/PMBUS address to 0x18.

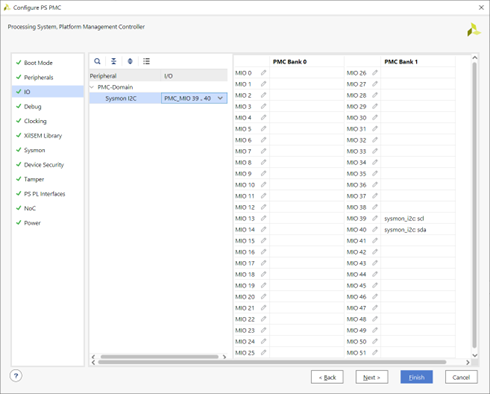

Go to the IO tab and set the Sysmon I2C to PMC_IO_39 .. 40

Click Finish

Continue to add any FPGA IP / logic as you would for a normal design, create your block design wrapper file and build the FPGA.

Step 4 – Test the changes

Set the active fan control to be System Controller managed by setting the physical jumpers on the board for the fan tachometer jumper J348 Pin 1-2 and fan control jumper J347 Pin 1-2.

Power up the board and programme it.

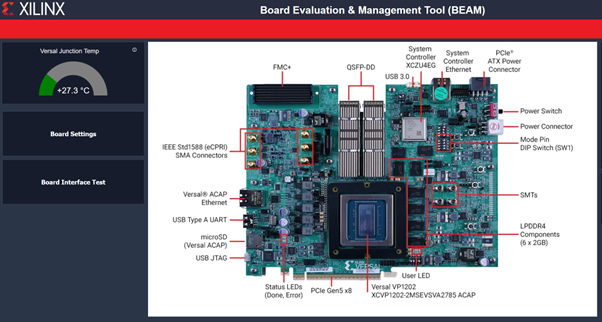

Confirmation that the changes have worked will be visible from the BEAM interface where the temperature will now be displayed, but more importantly the reduction in fan speed should be more audibly pleasing.

Note: I have found that the firmware on the system controller is not rock solid, this means that at times the data link can fail. I've only observed it fail safe (the fan will spin back up to maximum) so it's not a massive issue other than the increased volume. If this happens you can reset just the system controller by pressing the SYSCTL_POR_B button on the board. It seems to happen most often in the debug phase when you are resetting the Versal multiple times, and it seems to happen less if the board is left to settle for a while after initial power on before performing subsequent resets.

Note: References to Xilinx have been updated with AMD in line with their branding transition.

How ITDev can help you

This blog article is just one small demonstration of how we keep clients informed: documenting the steps required to reproduce the same set-up as we used.

We can assist you in achieving your goal and solving your problem.

- There will be open, frequent communication as we look to understand your aims.

- In-line with your needs, you will be kept up to date on progress.

- Appropriate knowledge transfer activities will occur throughout the project.

If you have any questions or would like to find out how we can help you with your product development journey, initial discussions are always free of charge. We would be delighted to speak to you so please contact us.

Main image: Overlay silent smiley icon created by Freepik - Flaticon